Sondrel开发性能验证环境以快速创建ASIC

英国雷丁,2021年11月3日。创建定制ASIC(专用集成电路)的一个重要阶段是验证定制ASIC是否以可能达到的最佳方式完成其任务。一般可通过合成并运行RTL来验证,判断ASIC的运行情况是否符合最初设定的性能规范。经过调整设计后,其性能会随着每次RTL运行有所提升,但每个迭代周期都需要数周才能产生影响。

Sondrel开发了一种名为性能验证环境(PVE)的方法,据此创建Synopsys®SystemC仿真模型,并通过模型调整各类参数,从而了解参数变化对性能规范的影响。每个变量无需花费过长时间即可建模并在数小时内运行,而若是尝试使用RTL仿真则需数周时间。RTL仿真日益精确,但相比于这种新的建模方式在数日内即可达到最佳配置的速度而言,其精确度就显得微不足道了。精确度和速度之间已经达成了一定的平衡。这使得Sondrel借助配置方便快速且风险较小的优点,成功为客户创建了许多项目。

该方法首先使用勘探平台获取并导出所有交易追踪结果到Sondrel的PVE,该PVE使用了基于Synopsys VCS®、Synopsis DVE、Synopsys Verdi®产品的Python-in-SystemC内嵌技术。它还可以作为Mentor ®Questa™ 和Cadence® Xcelium™ 等其他EDA供应商的支持工具。

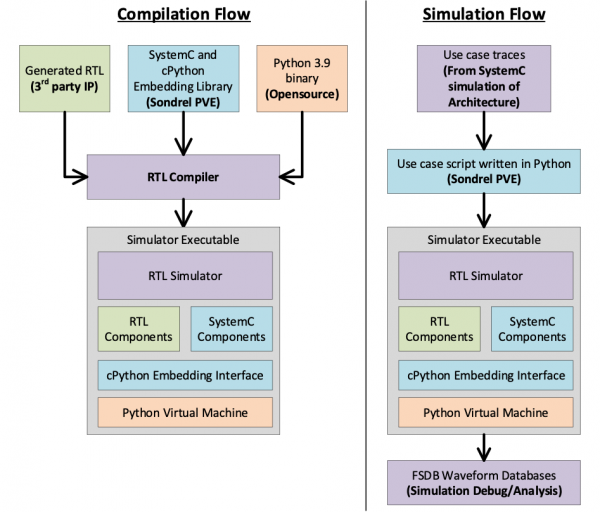

PVE插图左侧即为PVE的测试台编译流程,使用了某知名EDA供应商的RTL编译器。该编译器采用Sondrel PVE(由SystemC和Python代码构成),并将其与生成的RTL和Python3.9的二进制(可作为开源工具)相结合,由此创建模拟器屏幕截图应用程序,即运行测试的最终可执行程序。

如流程图右侧所示,在运行该程序时,自周期精确的SystemC仿真架构的选取使用案例追踪,系统架构师提供脚本读取追踪信息,并以FSDB波形数据库的输出进行仿真运用。如有必要,可以使用Verdi、DVE、Questa和Xceium定义的标准工具和方法进行调试。

该方法的优势在于,由于RTL仿真可提供详尽的仿真细节,可以暴露勘探平台上并不明显的RTL问题。此外,整个流程也可以在UVM环境准备就绪前完成,提前明确RTL的运行状态。多数情况下,和获取System Verilog-UVM知识相比,它在获取Python知识时更易操作,因此这种方法对架构师和性能工程师而言非常便捷易行。

有关更深入讨论PVE的文章,请点击 此处。

关于SondrelTM

Sondrel成立于2002年,是集成电路各阶段设计方面值得信赖的合作伙伴。 其在定义和设计专用集成电路方面的咨询能力屡获殊荣,为其将设计转化为经过测试的批量封装硅芯片的一站式服务提供了有力补充。整个供应链流程的单点联系,确保风险低,上市时间快。Sondrel总部位于英国,其通过在中国、印度、法国、摩洛哥和北美的办事处,为全球客户提供支持。更多信息,请访问www.sondrel.com

新闻联系人:

Nigel Robson, Vortex PR nigel@vortexpr.com +44 1481 233080

Sondrel和架构未来是Sondrel Limited的商标

Questa是商标,Mentor是Mentor的注册商标

Xceium是商标,Cadence是Cadence的注册商标

Synopsys、Verdi、VSC是Synopsys的注册商标

所有其他商标均是其各自所有者的注册商标